Contrôleurs de mémoire Flash pour des solutions industrielles

16 novembre 2018Dernière modification: 13 août 2019

Introduction

Les mémoires de masse GOODRAM Industrial pour des applications industrielles se caractérisent par une haute fiabilité, une grande durabilité et une large gamme de températures de fonctionnement. Ces caractéristiques sont obtenues grâce à un design qui prend en compte les spécifications et les attentes du client. Répondre à ces attentes est impossible sans sélection et validation des composants. Dans ce processus, une attention particulière est accordée au contrôleur de mémoire et à ses propriétés garantissant un fonctionnement sans problèmes à long terme.

Gestion de la mémoire NAND flash

L’utilisation de NAND FLASH dans les mémoires de masse nécessite un certain nombre de techniques d’optimisation.  L’une des principales techniques d’optimisation est la translation de l’adresse du secteur de disque vers l’adresse physique de la page de mémoire (logical to physical mapping). Cela est nécessaire car l’hôte (ordinateur) adresse la mémoire en utilisant des secteurs de taille 512 o, tandis que la taille d’une page NAND FLASH standard est de 8 ou de 16 ko et il n’est pas possible de reprogrammer la page sans supprimer le bloc de mémoire entier. Le bloc de mémoire contient 256 à 512 pages, le mécanisme de translation d’adresses doit donc interagir avec l’algorithme de tri (garbage collection). Le tri des données consiste à défragmenter les blocs de mémoire. En conséquence, les données à jour sont transférées vers des pages de mémoire libres de manière à remplir le bloc. Tout bloc contenant des données obsolètes est supprimé et préparé au ré-enregistrement. Une distribution uniforme des cycles d’enregistrement entre tous les blocs de mémoire NAND FLASH est assurée par l’algorithme wear leveling. Celui-ci est basé sur des compteurs de cycles d’enregistrement/de programmation (p/e) de blocs de mémoire. Tous les algorithmes susvisés incluent une carte des blocs endommagés. Cette carte est créée au moment de l’initialisation de la mémoire de masse et peut être étendue ultérieurement avec les blocs hors usage, appelés « run time bad block » ou « later bad block ». La structure et la haute fiabilité des algorithmes d’optimisation implémentés dans GOODRAM Industrial garantissent la performance de fonctionnement des mémoires de masse tout au cours de leur exploitation spécifique.

L’une des principales techniques d’optimisation est la translation de l’adresse du secteur de disque vers l’adresse physique de la page de mémoire (logical to physical mapping). Cela est nécessaire car l’hôte (ordinateur) adresse la mémoire en utilisant des secteurs de taille 512 o, tandis que la taille d’une page NAND FLASH standard est de 8 ou de 16 ko et il n’est pas possible de reprogrammer la page sans supprimer le bloc de mémoire entier. Le bloc de mémoire contient 256 à 512 pages, le mécanisme de translation d’adresses doit donc interagir avec l’algorithme de tri (garbage collection). Le tri des données consiste à défragmenter les blocs de mémoire. En conséquence, les données à jour sont transférées vers des pages de mémoire libres de manière à remplir le bloc. Tout bloc contenant des données obsolètes est supprimé et préparé au ré-enregistrement. Une distribution uniforme des cycles d’enregistrement entre tous les blocs de mémoire NAND FLASH est assurée par l’algorithme wear leveling. Celui-ci est basé sur des compteurs de cycles d’enregistrement/de programmation (p/e) de blocs de mémoire. Tous les algorithmes susvisés incluent une carte des blocs endommagés. Cette carte est créée au moment de l’initialisation de la mémoire de masse et peut être étendue ultérieurement avec les blocs hors usage, appelés « run time bad block » ou « later bad block ». La structure et la haute fiabilité des algorithmes d’optimisation implémentés dans GOODRAM Industrial garantissent la performance de fonctionnement des mémoires de masse tout au cours de leur exploitation spécifique.

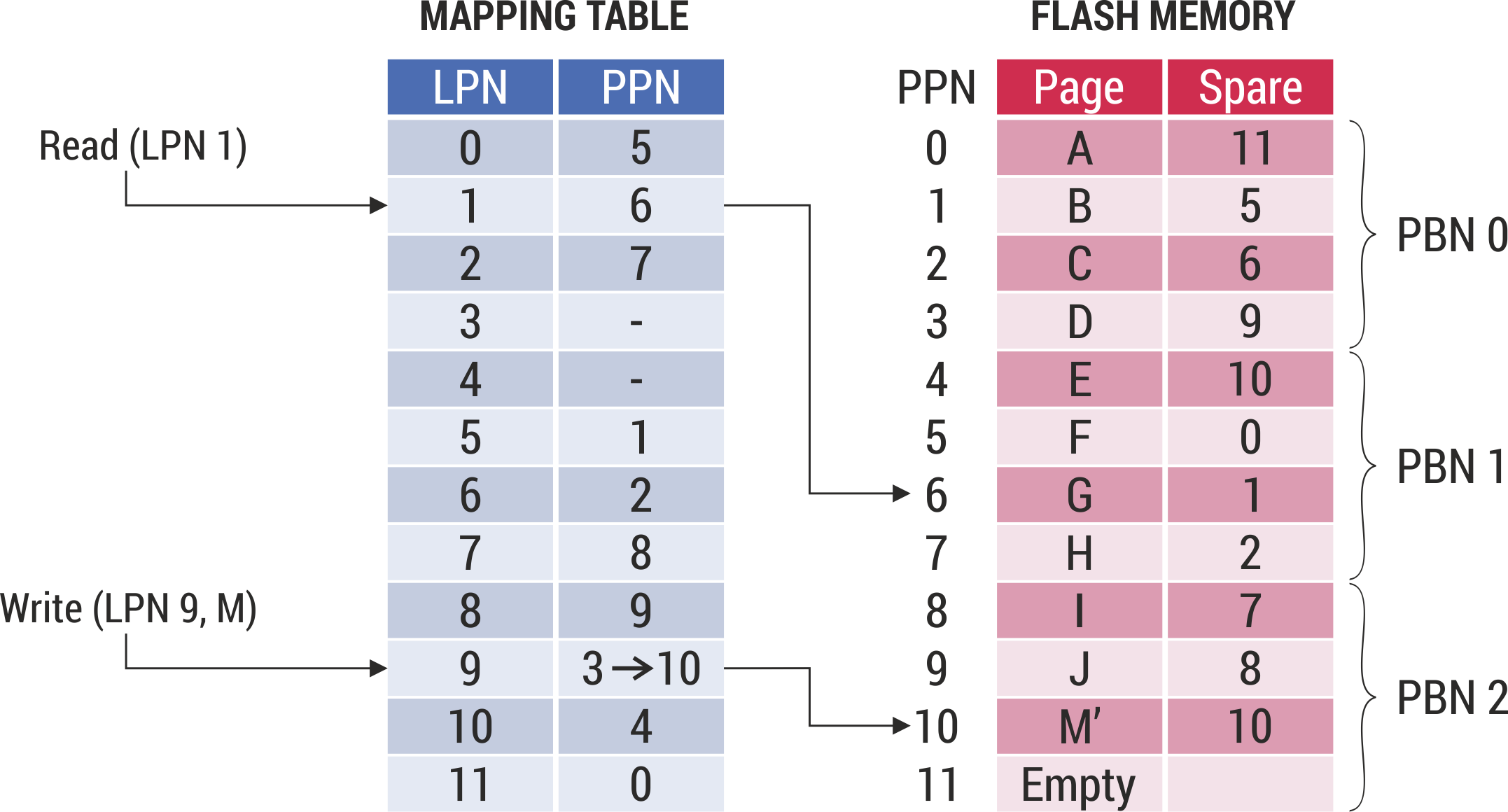

Flash translation layer

Les contrôleurs de disques SSD contiennent un FTL implémenté de type page mode mapping. Au cours d’un cycle d’enregistrement/de lecture d’un secteur de données, le numéro de page logique (LPN) est calculé. Le numéro de page logique est converti en numéro de page physique (PPN). Cette translation est effectuée à l’aide d’un tableau de mappage (Mapping Table).  Le tableau de mappage stocke les informations permettant de sélectionner correctement la puce mémoire, le noyau et le bloc de mémoire physique (PBN). L’avantage d’un FTL de type page mapping mode est sa grande vitesse et un faible facteur d’amplification de l’écriture. Les contrôleurs de cartes SD offrent aussi une deuxième méthode de translation block mode mapping. Le principe du block mode mapping est analogue à celui évoqué précédemment, à la différence près qu’un tableau de mappage contient les adresses des blocs. Le choix d’une méthode de translation dépend de la puce de mémoire NAND FLASH utilisée et de la vitesse de fonctionnement attendue.

Le tableau de mappage stocke les informations permettant de sélectionner correctement la puce mémoire, le noyau et le bloc de mémoire physique (PBN). L’avantage d’un FTL de type page mapping mode est sa grande vitesse et un faible facteur d’amplification de l’écriture. Les contrôleurs de cartes SD offrent aussi une deuxième méthode de translation block mode mapping. Le principe du block mode mapping est analogue à celui évoqué précédemment, à la différence près qu’un tableau de mappage contient les adresses des blocs. Le choix d’une méthode de translation dépend de la puce de mémoire NAND FLASH utilisée et de la vitesse de fonctionnement attendue.

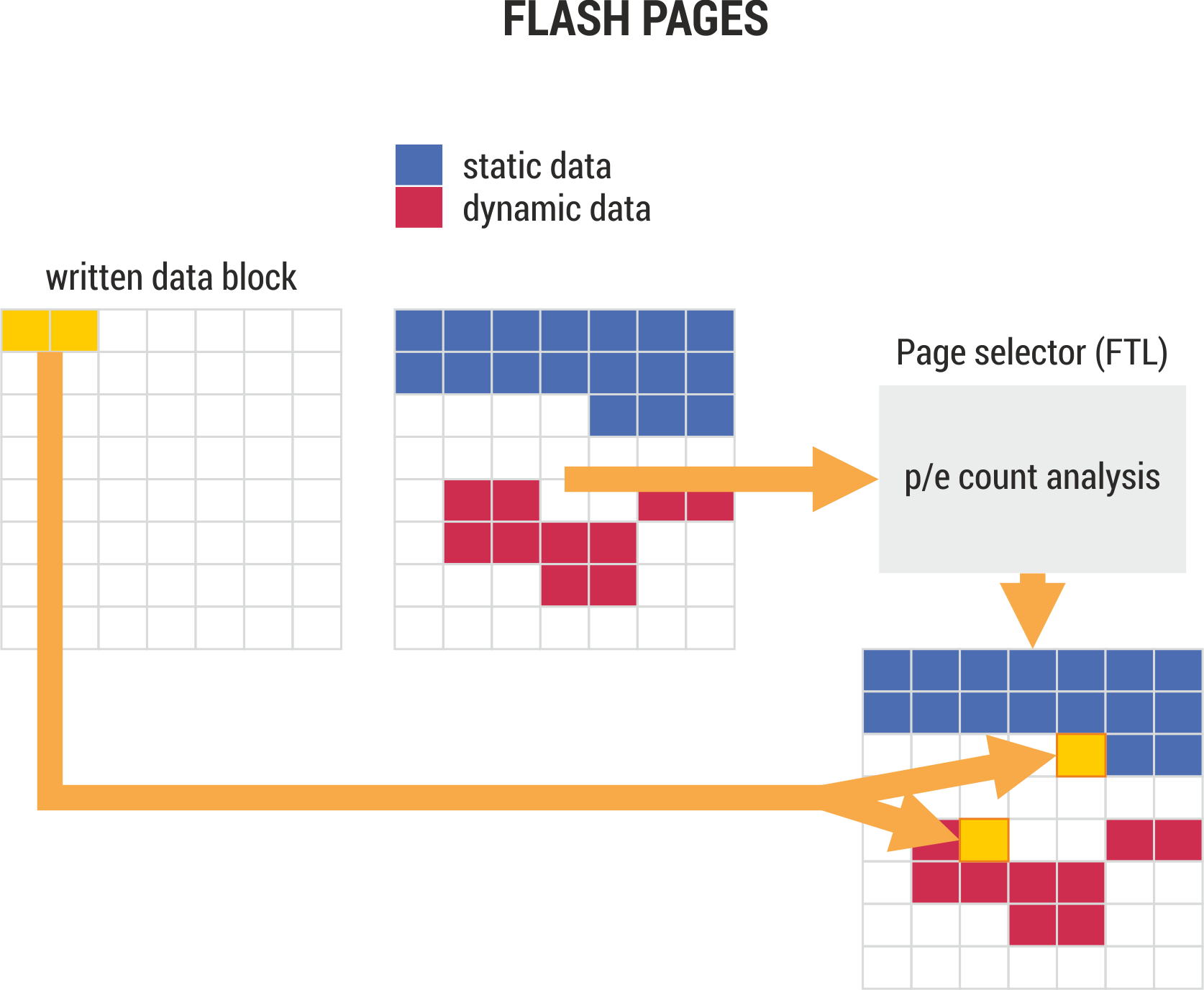

Wear leveling

Tous les contrôleurs utilisés dans les mémoires de masse GOODRAM Industrial appliquent un algorithme wear leveling statique et dynamique. La stratégie stockée dans l’algorithme wear leveling offre un choix de blocs de mémoire permettant de réduire les différences entre les nombres de cycles p/e dans tous les blocs de mémoire. Cet objectif est atteint en modifiant la localisation des données statiques et en utilisant ces localisations pour l’enregistrement des données en rotation fréquente.

Tous les contrôleurs utilisés dans les mémoires de masse GOODRAM Industrial appliquent un algorithme wear leveling statique et dynamique. La stratégie stockée dans l’algorithme wear leveling offre un choix de blocs de mémoire permettant de réduire les différences entre les nombres de cycles p/e dans tous les blocs de mémoire. Cet objectif est atteint en modifiant la localisation des données statiques et en utilisant ces localisations pour l’enregistrement des données en rotation fréquente.

Surapprovisionnement

Le surapprovisionnement est supporté par tous les contrôleurs dans les mémoires de masse GOODRAM Industrial. Dans le cas des disques SSD et des systèmes d’exploitation supportant la commande TRIM, la taille du surapprovisionnement dynamique dépend de la disposition des partitions créées sur le disque, ce qui veut dire que l’espace non alloué aux partitions ou l’espace n’ayant pas de fichiers attribués est automatiquement utilisé par le contrôleur pour augmenter le rendement et la durabilité de NAND FLASH. La taille prévue pour le surapprovisionnement peut également être définie par l’utilisateur à l’aide de tout outil de disque et de la commande ATA SET MAX ADDRESS, par exemple hdparm (Linux). Dans le cas d’un contrôleur de cartes SD, il n’est pas possible de configurer le surapprovisionnement. Dans ce cas, le rendement et la durabilité des cartes peuvent être augmentés en supprimant les secteurs de données avant leur écrasement (commande ERASE – CMD38).

ECC

Les contrôleurs de disques SSD et de cartes SD appliquent les méthodes de décodage dur et souple BCH, LDPC. La méthode BCH (S10, contrôleurs SD) est utilisée pour les mémoires planaires de type 2D. La méthode LDPC est utilisée pour la détection-correction des erreurs dans les mémoires de type 3D (pour le S11, également 2D). Dans le cas des contrôleurs SSD, des bits ECC supplémentaires sont générés et enregistrés sur des pages de mémoire autres que les données (RAID ECC). Si une erreur de données non corrigée est détectée, les bits ECC supplémentaires augmentent la probabilité de correction de cette erreur. Dans ce cas, les données corrigées sont enregistrées sur une autre page et le bloc contenant la page source est marqué comme inefficace.

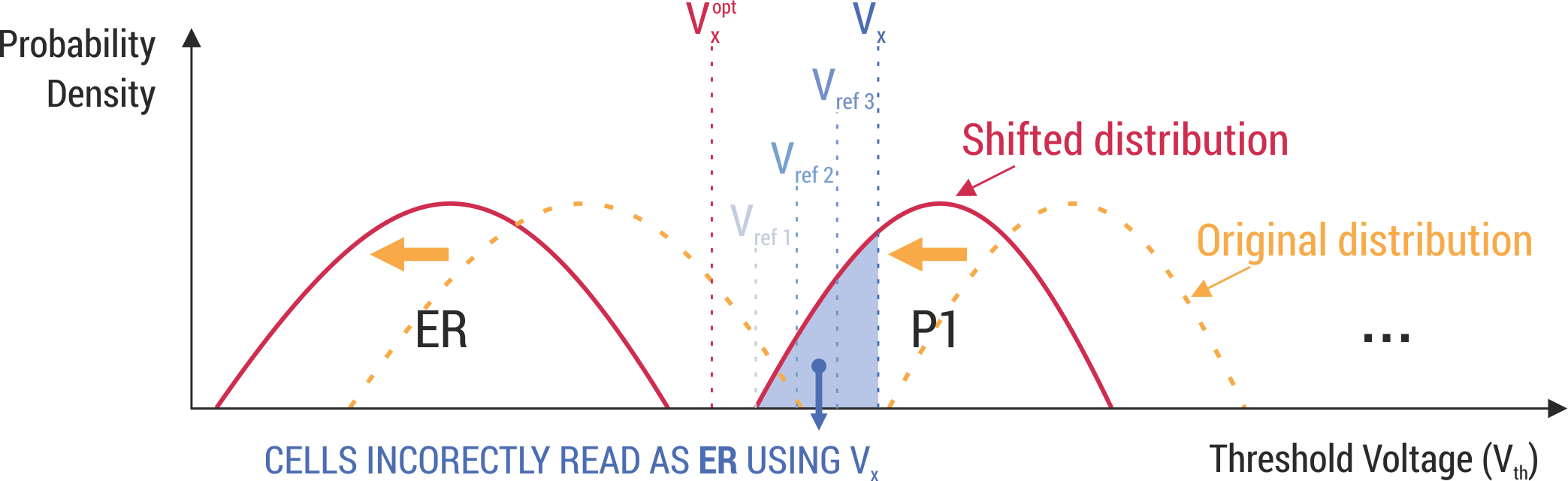

Read-retry

En cas d’erreurs de données non corrigées, les contrôleurs appliqués dans GOODRAM Industrial tentent de relire les données pour la valeur de tension de référence modifiée Vref. Les données lues sont corrigées en dur (BCH, décodage dur LDPC) peuvent être utilisées pour créer des statistiques de distribution de tension. Les statistiques de distribution de tension constituent la base pour le fonctionnement de l’algorithme de décodage souple LDPC.

En cas d’erreurs de données non corrigées, les contrôleurs appliqués dans GOODRAM Industrial tentent de relire les données pour la valeur de tension de référence modifiée Vref. Les données lues sont corrigées en dur (BCH, décodage dur LDPC) peuvent être utilisées pour créer des statistiques de distribution de tension. Les statistiques de distribution de tension constituent la base pour le fonctionnement de l’algorithme de décodage souple LDPC.

Protection contre une mise hors tension soudaine.

Le risque de perte de données à la suite d’une coupure de courant soudaine est minimisé par des méthodes propres à un contrôleur donné. Les contrôleurs S10 et S11 utilisent une stratégie limitant la quantité et la durée de stockage de données en mémoire cache. Le signal ACK confirmant l’enregistrement de données n’est généré qu’après la sauvegarde de données en mémoire principale FLASH. Ainsi, le risque d’une confirmation injustement positive de l’enregistrement de données est éliminé. De plus, dans le cas du contrôleur S10, il est possible de maintenir l’alimentation électrique au moyen de condensateurs au tantale. Le maintien de l’alimentation à l’aide de ces condensateurs est facultatif et nécessite une conception spéciale de circuits électriques. Les contrôleurs de cartes SD mettent en oeuvre une stratégie différente. En SD, l’enregistrement est effectué en double mémoire tampon. Apres la remise sous tension, les données sauvegardées en dernier sont vérifiées. Si, à cause d’une coupure de courant, des erreurs de données non corrigées se sont produites, l’écrasement des données d’origine est omis ou les données sont reconstituéesà partir du tampon.

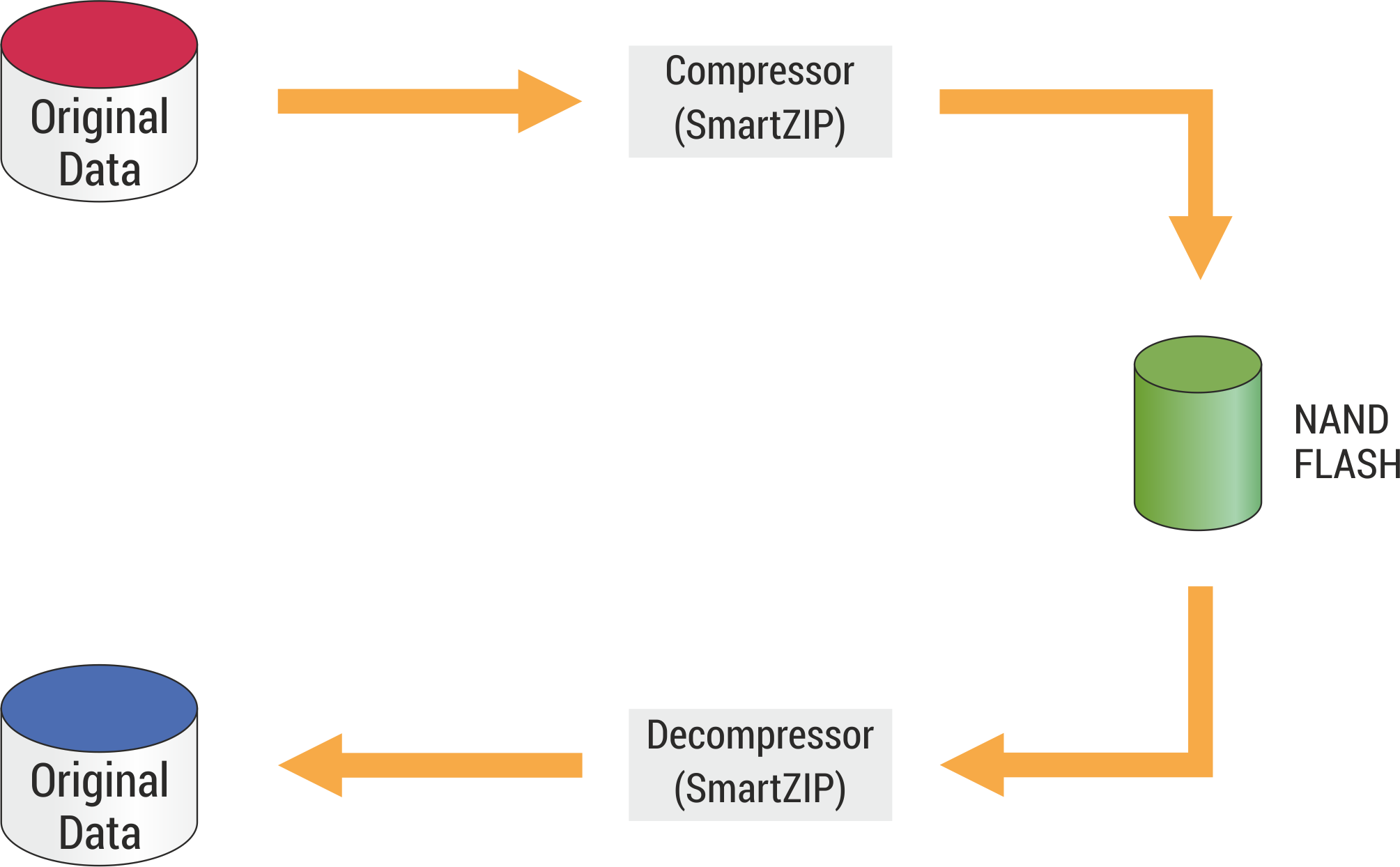

SmartZIP

La fonction SmartZIP consiste en une compression de données dans le cycle d’enregistrement et une décompression dans le cycle de lecture. Dans le cycle d’enregistrement, les données de la mémoire tampon d’enregistrement sont dirigées vers le bloc de compression. Dans ce bloc, leur taille est réduite. En fonction de l’entropie, la taille des blocs à enregistrer peut être réduite plusieurs fois. Les données compressées sont enregistrées dans NAND FLASH. Dans le cycle de lecture, nous avons affaire au cas inverse, c’est-à-dire que les données lues depuis NAND FLASH sont décompressées, puis transférées vers le tampon de lecture. Un avantage de la fonction SmartZIP est la rapidité de fonctionnement (la compression est effectuée en interne sans la participation de l’hôte) et une durée de vie plus longue de NAND FLASH.

Comparaison des contrôleurs

| Phison PS3110-S10 | Phison PS3111-S11 | Phison PS8210 | |

|---|---|---|---|

| Interface | SATA III | SATA III | SD 3.0 |

| Type de mémoire | MLC, TLC, 3D NAND | 3D NAND, TLC, MLC | 3D NAND, TLC, MLC |

| Canaux de mémoire | 8 | 2 | N/A |

| Type d’ECC | BCH | LDPC hard&soft decoding | BCH, LDPC hard&soft decoding |

| RAID ECC | OUI | OUI | OUI |

| FTL | Mode page mapping | Mode page mapping | Mode block/page mapping (selon l’application) |

| Mémoire cache | Jusqu’à 1 Go | néant | N/A |

| Cryptage | Supporté | Supporté | Supporté |

| Compression de données | NON | OUI | NON |

| Capacité | Jusqu’à 1 To | Jusqu’à 512 Go | Jusqu’à 512 Go |

| Vitesse séquentielle | 550/520 Mo/s | 550/500 Mo/s | 90/45 Mo/s |

| Vitesse aléatoire (4k) | 100k/90k IOPS | 100k/85k IOPS | Pas de données |

| Protection contre une mise hors tension soudaine | OUI (possibilité de montage de condensateurs supplémentaires) | OUI | Intégrée dans le logiciel |

| Attributs S.M.A.R.T. | OUI | OUI | OUI (en option) |

| NCQ | Jusqu’à 32 | Jusqu’à 32 | N/A |

| TRIM | OUI. Déterministe ou non déterministe (en fonction du FW) | OUI. Déterministe ou non déterministe (en fonction du FW) | N/A |

| Secure Erase | OUI | OUI | N/A |

| Surapprovisionnement | OUI | OUI | OUI |

| Capteur thermique | Supporté (en option) | Supporté (en option) | N/A |

| Gestion des blocs endommagés | Intégrée | Intégrée | Intégrée |

| Gestion de faible consommation de puissance | Mode DIPM/HIPM | Mode DIPM/HIPM | Basée sur le standard SD |

| Read retry | OUI | OUI | OUI |