Méthodes de détection et de correction d’erreurs dans les mémoires de masse

16 novembre 2018Dernière modification: 16 novembre 2018

Résumé

Les systèmes de mémoire NAND FLASH 3D trouvent actuellement un usage fréquent pour la production de disques SSD destinés aux applications bureautiques et domestiques. Cette technologie sera bientôt disponible pour les applications industrielles. C’est pourquoi il est utile de démontrer les différences entre la méthode de détection-correction d’erreurs appliquée dans les mémoires NAND FLASH de type 2D et NAND FLASH de type 3D.

L’introduction au présent article traite de la structure des systèmes de mémoire NAND FLASH de type 3D à un niveau élémentaire; ce qui est suivi d’une discussion sur les causes fondamentales des erreurs de données. Les méthodes de décodage dur et souple (hard et soft decoding) BCH et LDPC sont abordées dans le chapitre consacré aux méthodes de détection et de correction. Le résumé présente brièvement les tendances dans l’évolution des technologies. Cet article contient des références à des matériaux externes, permettant d’élargir la portée du sujet abordé.

Introduction

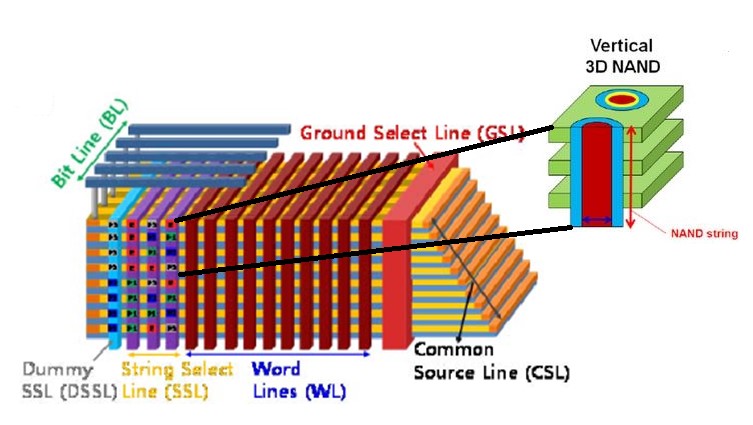

Les systèmes de mémoire NAND FLASH 3D doivent leur position sur le marché à leur grande durabilité et à leur prix relativement bas par Go. La durabilité des systèmes de mémoire de type 3D résulte de la structure des cellules de mémoire (fig. 1).

a.)

b.)

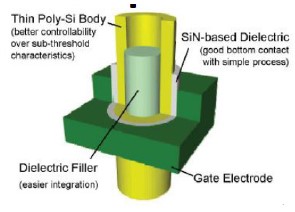

Fig. 1. Structure d’une cellule de mémoire a.) 2D b.) 3D

(représentation schématique, ouvrage propre d’après les matériaux: Toshiba, Micron, IEEE ISBN 978-1-4673-2475-5, Yasuhiko HONDA, US 2011/0128788 A1)

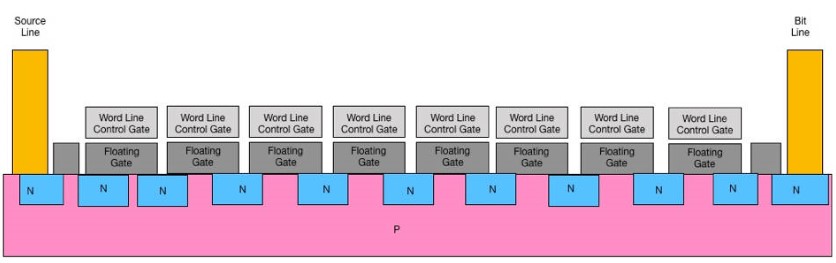

Une cellule de mémoire NAND FLASH 3D est un transistor vertical (fig. 1b). Dans une telle cellule, les informations sont enregistrées et stockées sous forme d’une charge électrique accumulée dans une grille flottante (nitrure – fig. 1b). La grille flottante, placée entre deux couches d’isolant (oxyde bloquant et oxyde tunnel – fig. 1b) entoure le canal polycristallin du transistor (corps poly-si – fig. 1b). En conséquence, la surface et donc la capacité de la grille flottante est supérieure à celle d’une cellule de mémoire réalisée en technologie 2D (fig. 1a), son épaisseur est également plus grande.

Les dimensions de la grille flottante influent sur ses paramètres électriques et sur la durabilité de la cellule de mémoire. Les systèmes de mémoire 2D MLC de 15 nm typiques ont une durée de vie de 3 000 cycles de réinitialisation / programmation et une perditance jusqu’à an pour une consommation maximale. À condition d’appliquer des méthodes appropriées de détection et de correction d’erreurs, ces paramètres correspondent à la durabilité des systèmes 3D TLC.

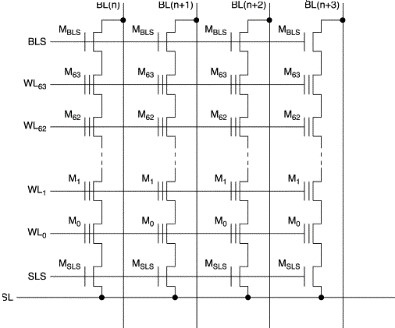

Les systèmes de mémoire 3D NAND FLASH doivent leur grande capacité à une structure multi-couches des cellules de mémoire (fig. 2).

a.)

b.)

c.)

d.)

Fig. 2. Représentation schématique de la structure NAND FLASH a.) matrice des cellules de mémoire 2D; b.) matrice des cellules de mémoire 3D; c.) chaîne de cellules de mémoire 2D; d.) structure des cellules de mémoire 3D (ouvrage propre d’après les matériaux: Toshiba, Micron, IEEE ISBN 978-1-4673-2475-5, Yasuhiko HONDA, US 2011/0128788 A1)

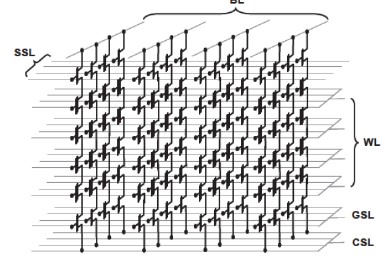

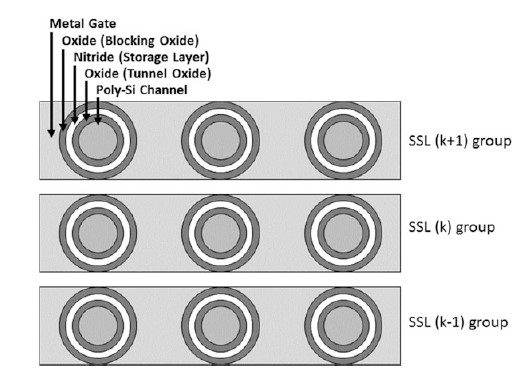

Comme le montre la figure 1b, les cellules de mémoire 3D forment des transistors verticaux. Ces transistors sont fabriqués sur un substrat commun, dans le processus d’irradiation multiple, de gravure et de dopage. Après leur fabrication, ils forment des piles verticales, composées de plusieurs dizaines de couches (96 couches et plus) (fig. 2b). Les piles sont adjacentes (fig. 3).

Fig. 3. Vue horizontale des cellules de mémoire 3D (représentation schématique, ouvrage propre d’après les matériaux: Toshiba, Micron, IEEE ISBN 978-1-4673-2475-5)

Une telle structure assure une grande condensation en termes de capacité de données pour chaque mm2 de la structure du semi-conducteur. Dans ce cas (3D), les paramètres technologiques ne sont pas exprimés en nm, car la capacité du système de mémoire dépend essentiellement du nombre de couches et de leur structure. La technologie 3D n’est pas dénuée d’inconvénients, qui seront abordés dans le chapitre suivant.

Sources d’erreurs dans NAND FLASH

De nombreuses ressources bibliographiques décrivent la structure des mémoires de masse construites sur la base de la technologie NAND FLASH. Quelle que soit l’interface (USB, SATA, PCIe), chacune d’elles contient un bloc de détection et de correction des erreurs de données. Les erreurs de données résultent de la distribution des cycles d’enregistrement, de lecture, de suppression, de perditance, de SILC (ang. stress induced leakage current), de charge de-trapping, de dommages permanents et temporaires (travail collectif Multi-Level Cell Flash Memory Fault Testing and Diagnosis IEEE ISBN: 0-7803-9359-7 ; JEDEC JEP122G). Ils sont une conséquence naturelle de la structure des systèmes de mémoire et ses technologies utilisées, si l’on peut dire de leurs « défauts ».

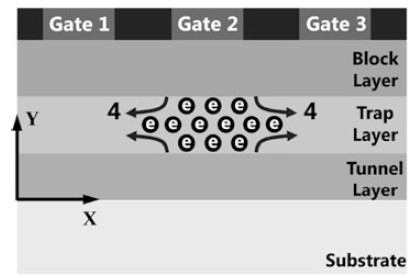

La technologie 3D NAND FLASH, relativement nouvelle, n’élimine pas les défauts de son prédécesseur 2D. Elle introduit de nouveaux défis liés à la perditance dans la structure verticale. Dans le cas de la mémoire 3D, on peut distinguer les perditances, déjà connues de la technologie 2D, vers: le canal du transistor, la grille, ainsi que de nouvelles, vers : les couches intermédiaires (ang. spacers), les chaînes de cellules de mémoire, ainsi qu’à travers la couche partagée avec la grille flottante (trap layer – fig. 4).

Fig. 4. Perditance entre les cellules de mémoire adjacentes (représentation schématique, ouvrage propre d’après : Micheloni, Rino, Crippa, Luca, Marelli, Alessia, Inside NAND Flash Memories, ISBN 978-90-481-9431-5)

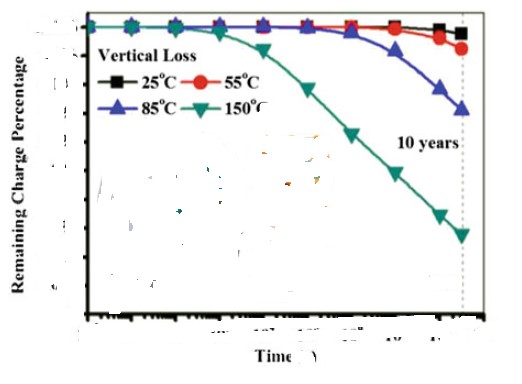

La perditance est fortement tributaire de la température, ce qui est illustré sur la figure 5.

Fig. 5. Tendance illustrant la relation entre le temps de perditance et la température (ouvrage propre)

De plus, dans les structures 3D, les cellules de mémoire situées sur les couches supérieures peuvent avoir des dimensions et des paramètres différents de ceux des cellules situées sur les couches inférieures. Il en résulte que les systèmes de mémoire 3D nécessitent des méthodes de détection et de correction d’erreurs différentes de celles pour la mémoire de type 2D.

Méthodes de détection et de correction d’erreurs

Les mémoires de masse basées sur la technologie NAND FLASH appliquent les méthodes de détection-correction BCH ou LDPC. Le nom BCH provient des noms des créateurs de la méthode Bose-Chaudhuri-Hocquenghem et est utilisé pour détecter et corriger les erreurs dans les mémoires de type NAND FLASH 2D (Varsha Regulapati, B.E., Error Correction Codes in NAND Flash Memory, University of Texas at Austin).

Les codes BCH appartiennent au groupe de codes par bloc cycliques (polynomiaux). BCH est un code de la même longueur que le mot de code n, contenant k éléments d’information. Le nombre d’éléments de contrôle est de n-k (fig. 6).

Fig. 6. Bloc de données divisé en k éléments d’information et en n-k éléments de contrôle (ouvrage propre sur base bibliographique)

Chaque enregistrement de données sur le disque entraîne la génération de mots de code par le contrôleur du disque, puis leur sauvegarde sur les pages du système de mémoire NAND FLASH (fig. 7).![]()

Fig. 7. Exemple de division d’une page du système de mémoire NAND FLASH en blocs (secteurs)

Comme on peut le voir, lors de l’enregistrement sont générés les éléments de contrôle appelés bits « ECC ». Leur sauvegarde requiert une capacité de mémoire supplémentaire. Chaque page du système de mémoire NAND FLASH dispose d’un espace dédié à cet effet, nommé « spare area ». Par exemple, une page de 16 Ko de mémoire peut contenir 1 Ko d’espace supplémentaire.

Dans le cycle de lecture, le mot de code est lu à partir de la puce de mémoire, puis le décodeur détermine le nombre de bits contenant des distorsions et leur emplacement, les bits déformés sont corrigés.

Les contrôleurs de disques SSD typiques permettent la détection et la correction de 64 à 72 bits dans tout secteur d’une taille de 1 ko (mémoire TLC 2D) et de 24 à 40 bits dans un secteur de 1 ko – MLC 2D. La fonction de détection et de correction d’erreurs par BCH peut être déterminée par des méthodes analytiques – il en est tout à fait autrement dans le cas des codes LDPC.

Les codes LDPC (ang. Low-Density Parity Check) appartiennent au groupe de codes en ligne. Le mot de code est créé au moyen de la matrice de génération G. Cela s’effectue en multipliant le vecteur de données par la matrice : v = u*G. Dans le cas des codes LDPC, aucun algorithme efficace permettant de déterminer la distance de Hamming entre deux mots de code n’a encore été trouvé. C’est pourquoi la détermination de l’efficacité approximative de détection et de correction d’erreurs par LDPC n’est possible qu’avec des méthodes statistiques.

Dans le cas de la LDPC, il existe deux méthodes de détection et de correction des erreurs de données, la première étant le « hard decoding » et la deuxième « soft decoding » (SM2258/59 Silicon Motion).

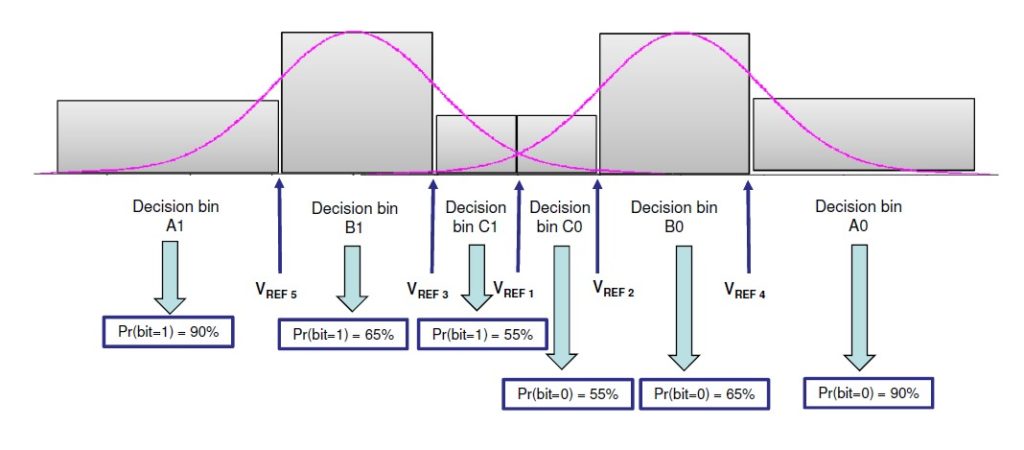

La méthode de hard decoding consiste en une lecture unique des données de NAND FLASH et en leur envoi à l’entrée du décodeur. L’efficacité de détection/correction par cette méthode est légèrement supérieure à celle de la BCH. Dans une situation où il est possible de modifier la tension de référence Vref et de relire les données de NAND FLASH, il est possible de créer des informations statistiques indiquant la probabilité de survenance d’une erreur (fig. 8).

Fig. 8. Distribution des niveaux de tension et probabilité de lecture 0 ou 1

Les statistiques créées sont utilisées par l’algorithme itératif de détection-correction d’erreurs. Cet algorithme prend la décision de remplacer les bits par leurs contraires, c.-à-d. 0->1, 1->0, dans le but de minimiser la gravité du syndrome d’erreur.

Le principal avantage de la méthode soft decoding est la prise en compte de la statistique qui caractérise la perditance survenant dans NAND FLASH. En combinaison avec la technique d’enregistrement pSLC et pMLC, la technologie LDPC permet d’utiliser 3D NAND FLASH dans des applications industrielles exigeantes.

Pour récapituler

Dans le contexte d’un développement technologique continu, les limites de la technologie planaire ont déjà été atteintes en quelque sorte. Néanmoins, cette technologie est toujours prisée sur le marché industriel, où deux besoins et intérêts opposés se confrontent. D’une part, un nombre limité de fabricants pour lesquels la production de solutions 2D est peu rentable, d’autre part, des clients toujours en demande de solutions 2D, en raison de l’essor dynamique de l’automatisation des entreprises.

La solution pour cette situation d’impasse est de proposer une technologie 3D pour l’industrie, ce qui, ces dernières années, n’a pas été un succès, ou bien l’ampleur du processus n’était pas satisfaisante pour les fabricants de NAND FLASH. L’une des raisons de ce fait est le processus de validation. Les applications proposées actuellement se caractérisent par un cycle de vie de 5 ou 10 ans, ce qui empêche la mise à jour d’un élément aussi important que le Flash. La deuxième raison est la durabilité et la fiabilité de la technologie TLC 3D non encore confirmées au niveau MLC, ou celles de la technologie SLC, de plus en plus populaire dans les systèmes critiques – la plus ancienne et donc la plus chère.

Comme prévu par Wilk Elektronik, le marché va changer de façon spectaculaire au cours des cinq prochaines années – Nous constatons une demande croissante du secteur industriel pour des capacités plus élevées de nouveaux produits, comme par exemple les disques SSD au format M.2. Ceci est lié au développement continu des applications qui existent sur le marché depuis 5, 10, 15 ans déjà. Par conséquent, il est temps de remplacer les solutions de type CFast par des technologies basées sur une interface plus récente – déclare Wiesław Wilk, président de Wilk Elektronik.

D’autre part, l’automatisation des entreprises entraîne la nécessité de nouveaux investissements, dans lequel la mémoire joue un des rôles clés. Hélas, la technologie 2D MLC ou SLC devient de moins en moins disponible et ses coûts augmentent, ce qui explique la tendance de passer réellement au 3D TLC – un processus remarqué et activement soutenu par les fabricants tels que Toshiba. Notre société sera l’une des premières au monde à recevoir des échantillons de mémoire basés sur une technologie 3D TLC de qualité industrielle, en provenance de Toshiba – souligne le président. Une convention spécialement signée par Wilk Elektronik et Toshiba prévoit que ces échantillons puissent être convertis en modes pSLC ou pMLC, ce qui facilitera sans doute le travail des clients et répondra à leurs besoins. Il convient de souligner qu’au cours des 8 prochaines années, la technologie 3D TLC et les technologies connexes seront déjà appliquées dans la plupart des solutions de marché, nouvelles tout comme revalidées.

Préparé par:

Wilk Elektronik SA,

Fabricant de mémoires industrielles de les marqueurs GOODRAM et GOODRAM Industrial