Metody detekcji i korekcji błędów w pamięciach masowych

8 sierpnia 2018Ostatnia modyfikacja: 10 lutego 2023

Streszczenie

Układy pamięci NAND FLASH typu 3D obecnie i powszechnie stosuje się do produkcji dysków SSD dla zastosowań biurowo-domowych. Technologia ta wkrótce zawita do aplikacjach przemysłowych. Jest to powodem, dla którego warto zapoznać się z różnicami pomiędzy metodą detekcji-korekcji błędów stosowaną w pamięciach NAND FLASH typu 2D a NAND FLASH typu 3D.

We wstępie artykułu omówiono budowę układów pamięci NAND FLASH typu 3D w stopniu podstawowym, następnie zostały omówione podstawowe przyczyny powstawania błędów danych. W rozdziale poświęconym metodom detekcji i korekcji zostały omówione metody BCH oraz LDPC hard i soft decoding. Podsumowanie zostało poświęcone nakreśleniu trendu zmian technologicznych. W artykule znajdują się referencje do materiałów zewnętrznych, dzięki można poszerzyć zakres omawianej tematyki.

Wstęp

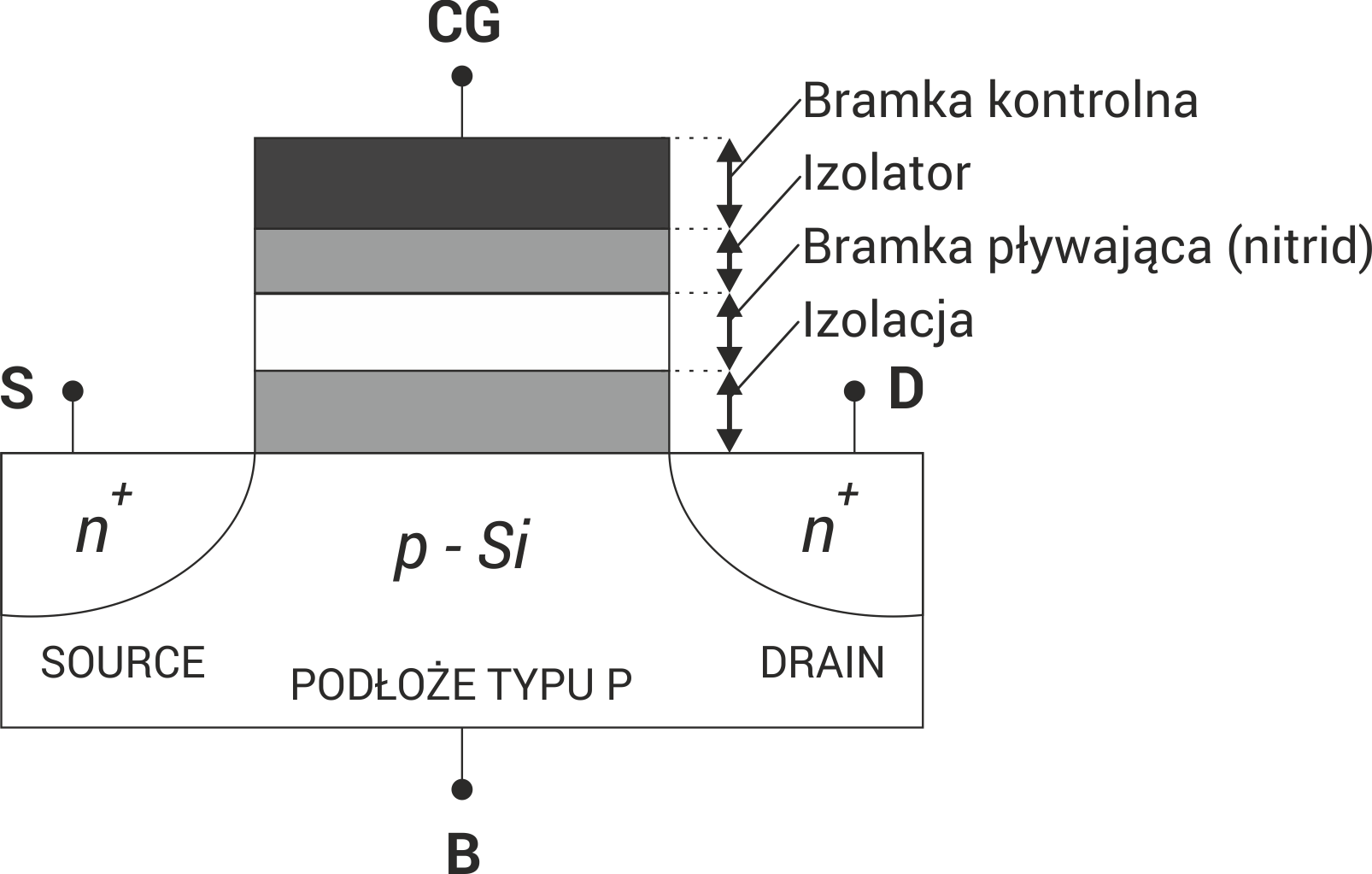

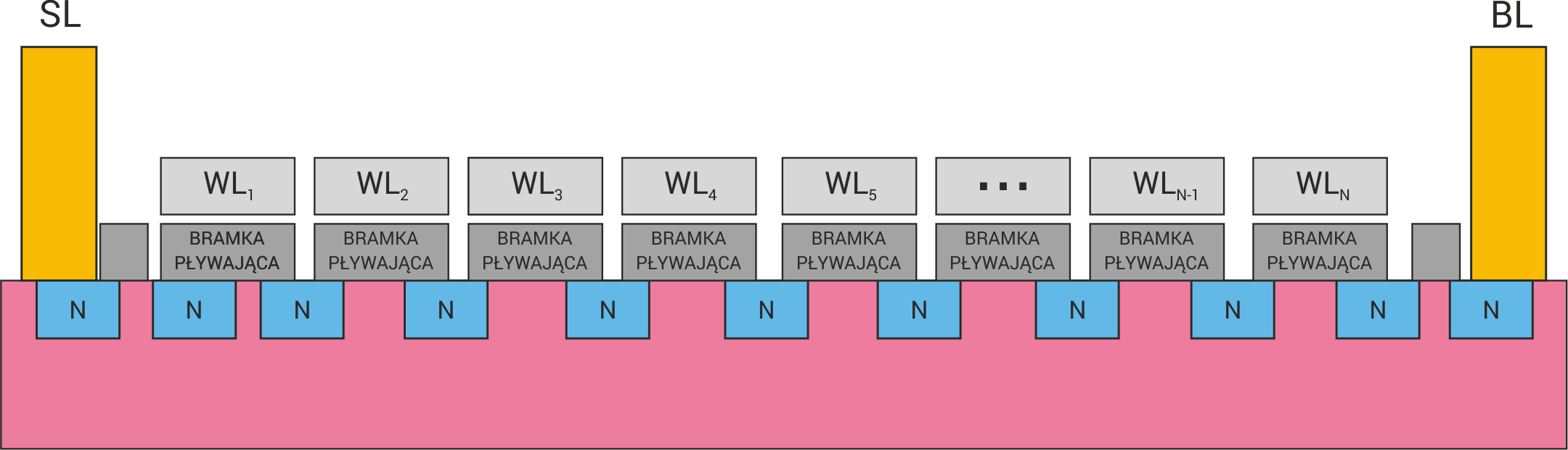

Układy pamięci NAND FLASH typu 3D zawdzięczają swoją pozycję rynkową dzięki dużej trwałości oraz relatywnie niskiej cenie za GB pojemności. Trwałość układów pamięci typu 3D wynika z budowy komórki pamięci (rys. 1).

a)

b)

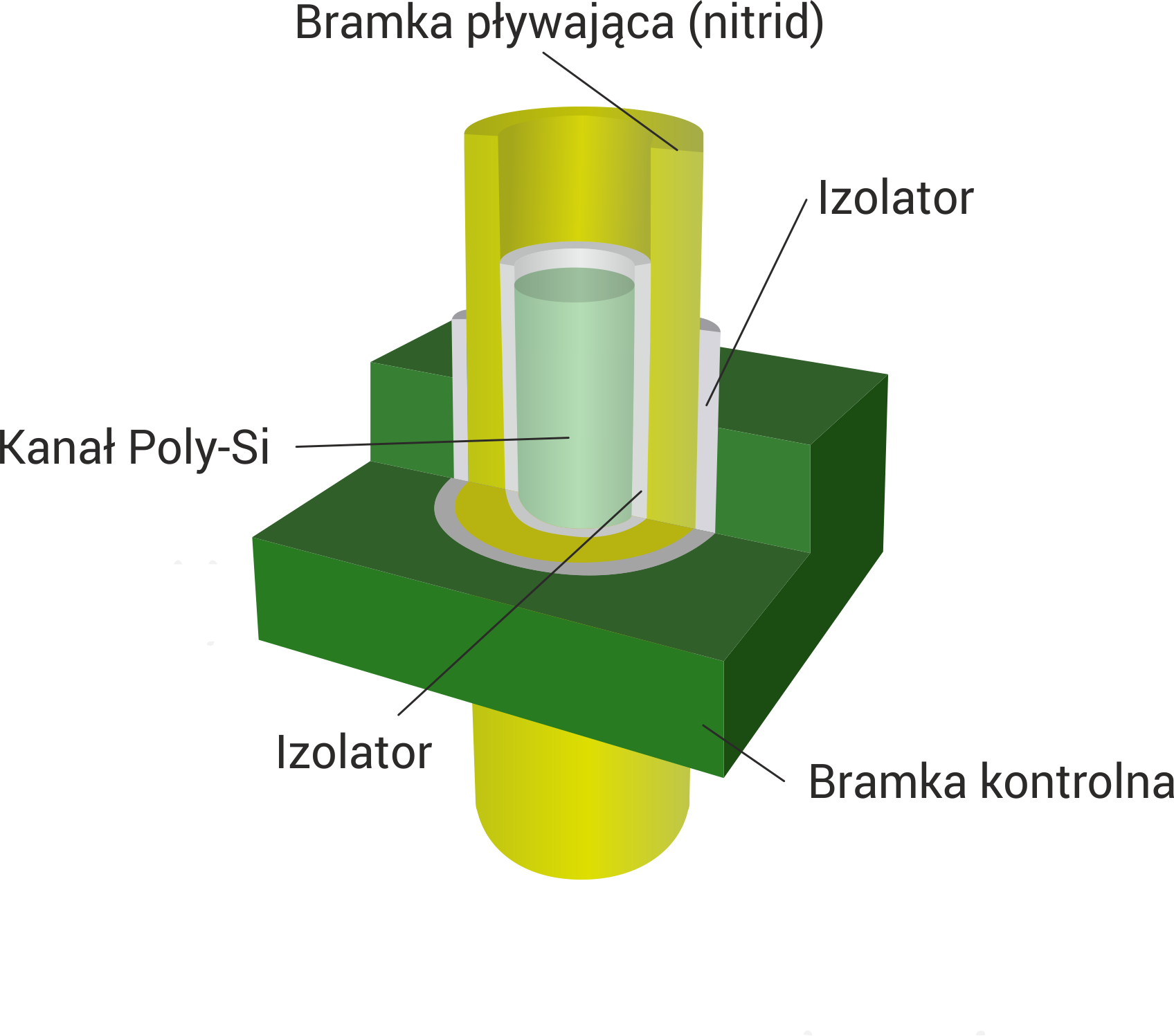

Rys. 1. Budowa komórki pamięci a) 2D b) 3D

(rysunek poglądowy, opracowanie własne na podstawie materiałów: Toshiba, Micron, IEEE ISBN 978-1-4673-2475-5, Yasuhiko HONDA, US 2011/0128788 A1)

Komórkę pamięci NAND FLASH typu 3D stanowi wertykalny tranzystor (rys. 1b). W tak zbudowanej komórce pamięci informacje są zapisywane i przechowywane w postaci ładunku elektrycznego zgromadzonego w pływającej bramce (nitride – rys. 1b). Pływająca bramka wraz z dwoma warstwami izolatora (blocking oxide i tunel oxide – rys. 1b) otacza polikrystaliczny kanał tranzystora (poly-si body – rys. 1b). W efekcie powierzchnia, a zatem pojemność pływającej bramki, jest większa, niż w przypadku komórki pamięci wykonanej w technologii 2D (rys. 1a), większa jest też jej grubość.

Wymiary bramki wpływają na jej parametry elektryczne i trwałość komórki pamięci. Typowe układy pamięci 2D MLC 15 nm cechuje trwałość 3000 cykli kasowania/programowania oraz upływność w maksymalnym stopniu zużycia wynosząca do jednego roku. Pod warunkiem zastosowania właściwych metod detekcji i korekcji błędów parametry te odpowiadają trwałości układów 3D TLC.

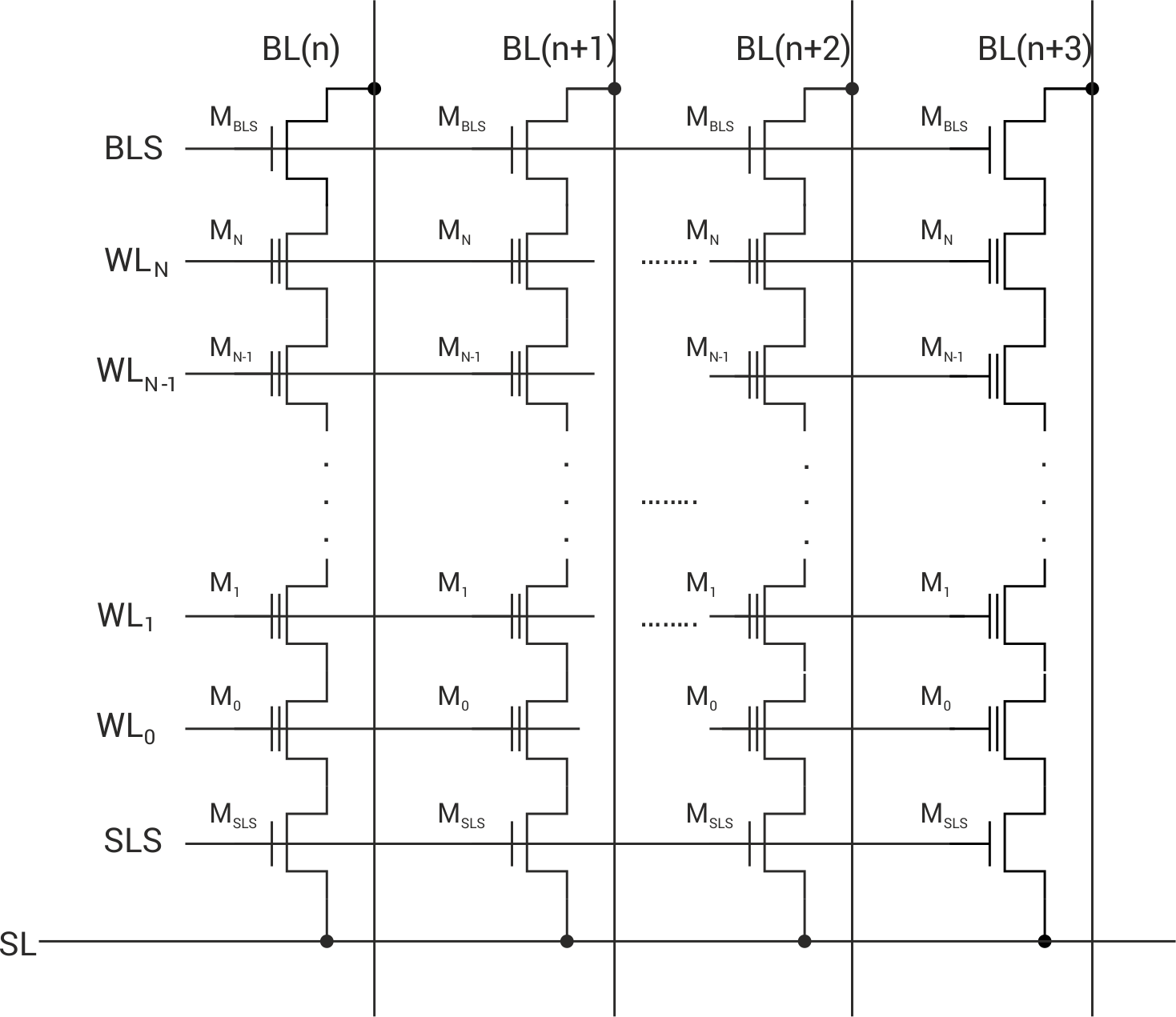

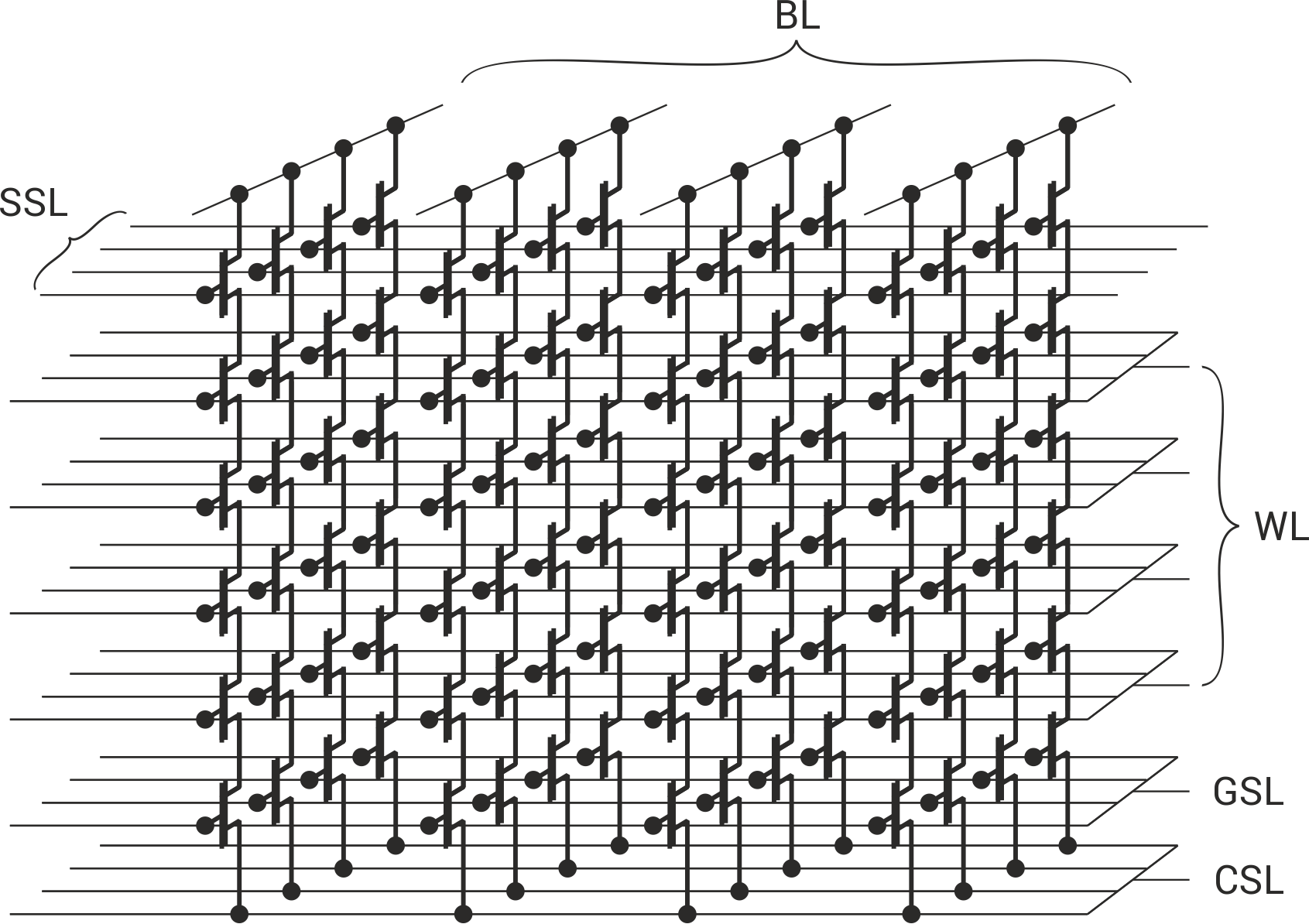

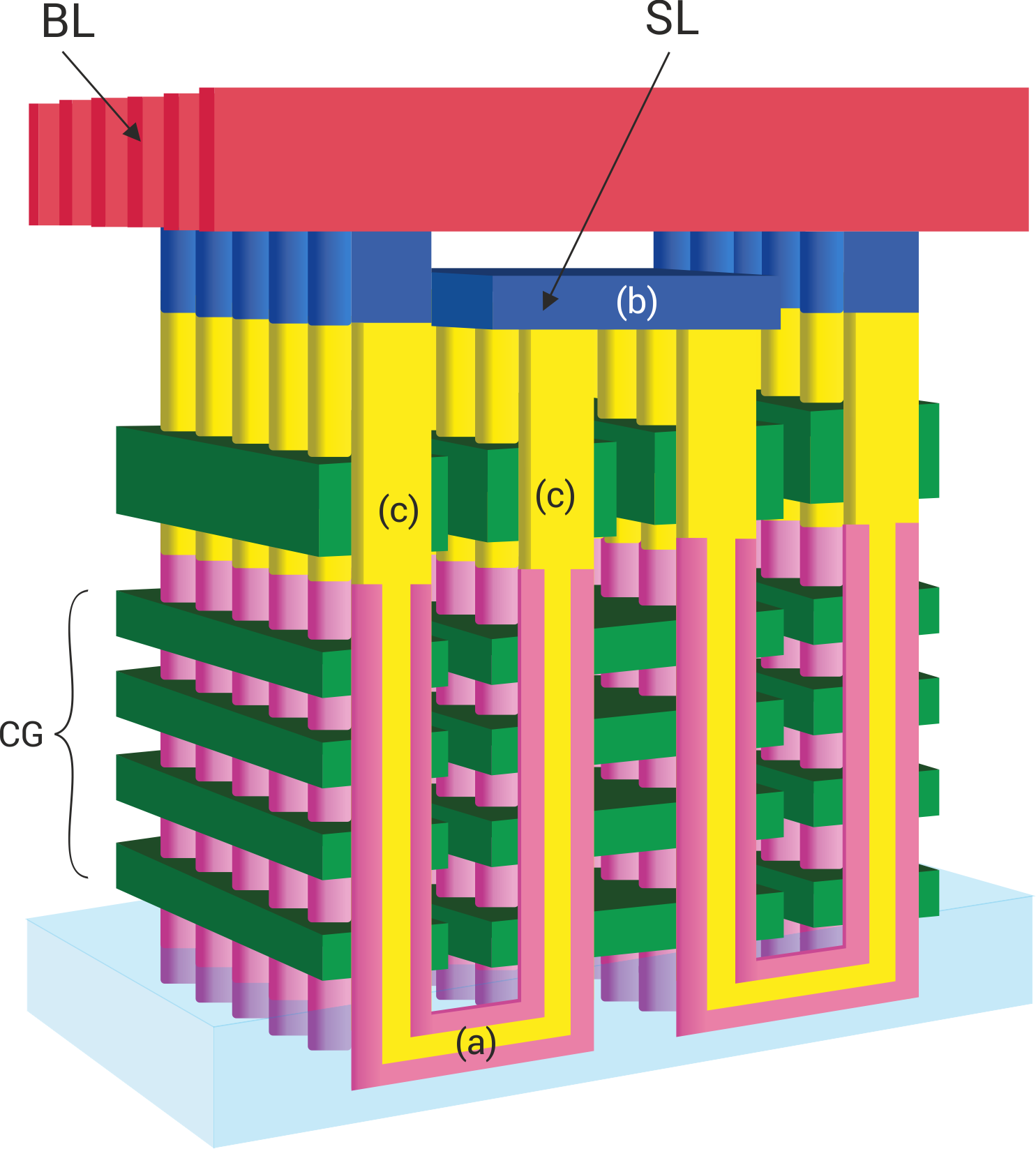

Układy pamięci 3D NAND FLASH zawdzięczają swoją dużą pojemność dzięki wielowarstwowej strukturze komórek pamięci (rys. 2).

a)

b)

c)

d)

Rys. 2. Rysunek poglądowy przedstawiający budowę NAND FLASH a) macierz komórek pamięci 2D; b) macierz komórek pamięci 3D; c) łańcuch komórek pamięci 2D; d) struktura komórek pamięci 3D

(opracowanie własne na podstawie materiałów: Toshiba, Micron, IEEE ISBN 978-1-4673-2475-5, Yasuhiko HONDA, US 2011/0128788 A1)

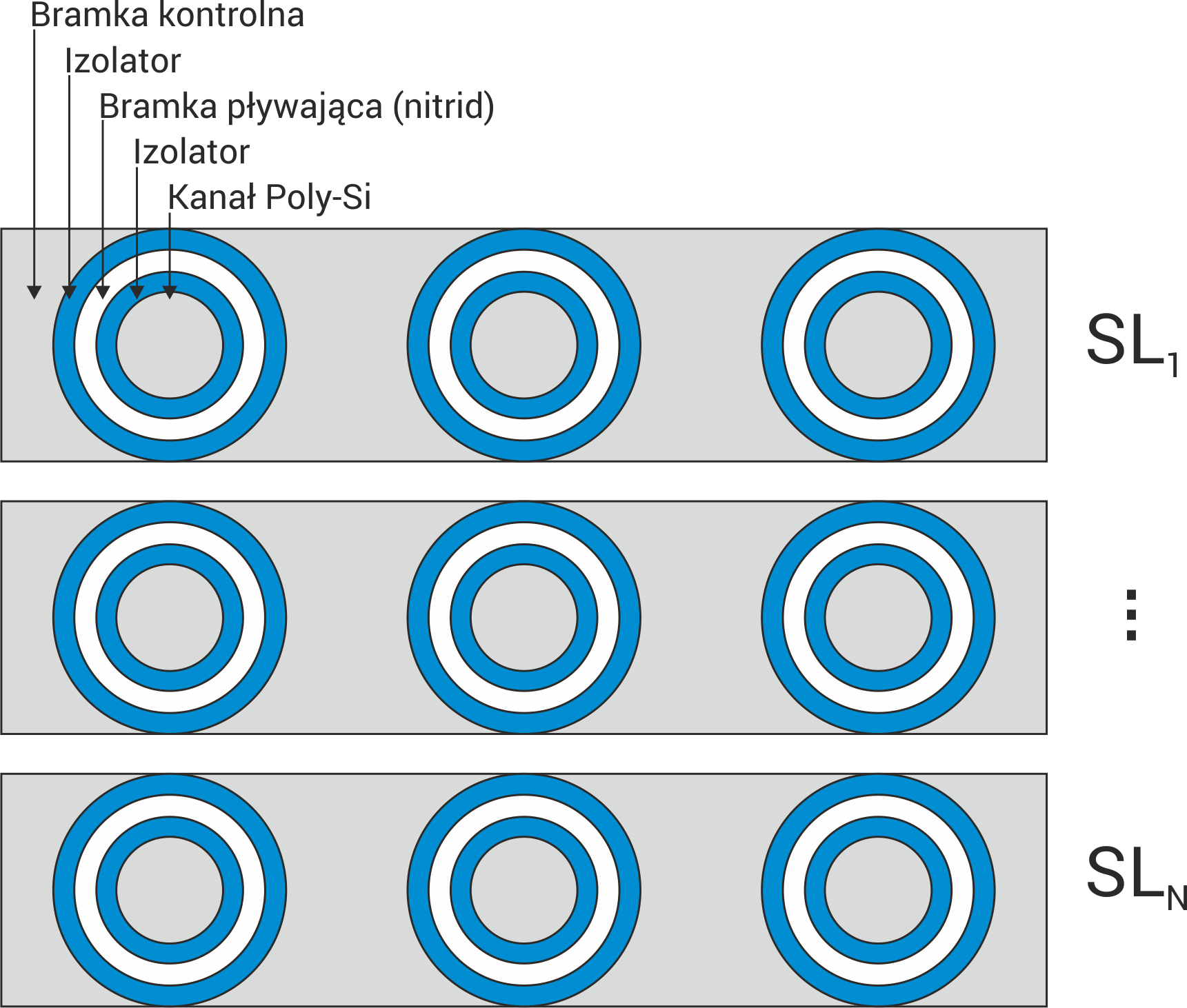

Jak zostało to zobrazowane na rysunku 1b, komórki pamięci 3D tworzą wertykalne tranzystory. Tranzystory te są wytwarzane na wspólnym podłożu, w procesie wielokrotnego naświetlania, trawienia, domieszkowania. Po ich wytworzeniu stanowią one pionowe (wertykalne) stosy, składające się z kilkudziesięciu warstw (96 i więcej warstw) (rys. 2b). Stosy umieszczone są sąsiadująco (rys. 3).

Rys. 3. Horyzontalny widok komórek pamięci 3D

(rysunek poglądowy, opracowanie własne na podstawie materiałów: Toshiba, Micron, IEEE ISBN 978-1-4673-2475-5)

Taka budowa zapewnia uzyskanie dużego upakowania pojemności danych na każdy mm2 struktury półprzewodnika. W jej przypadku (3D) nie podaje się technologii wykonania w nm, gdyż o pojemności układu pamięci decyduje głównie ilość warstw i ich struktura. Technologia 3D nie jest pozbawiona wad, o których będzie mowa w następnym rozdziale.

Źródła błędów w NAND FLASH

W obszernej literaturze możemy zapoznać się z budową pamięci masowych zbudowanych z zastosowaniem NAND FLASH. Niezależnie od interfejsu (USB, SATA, PCIe), każda z nich zawiera blok detekcji i korekcji błędów danych. Błędy danych powstają w wyniku dystrybucji cykli zapisu, odczytu, kasowania, upływności, SILC (ang. stress induced leakage current), charge de-trapping, uszkodzeń trwałych i przemijających (Praca zbiorowa Multi-Level Cell Flash Memory Fault Testing and Diagnosis IEEE ISBN: 0-7803-9359-7; JEDEC JEP122G). Są one naturalną konsekwencją budowy układów pamięci i zastosowanych technologii, można zaryzykować określenie „wad”.

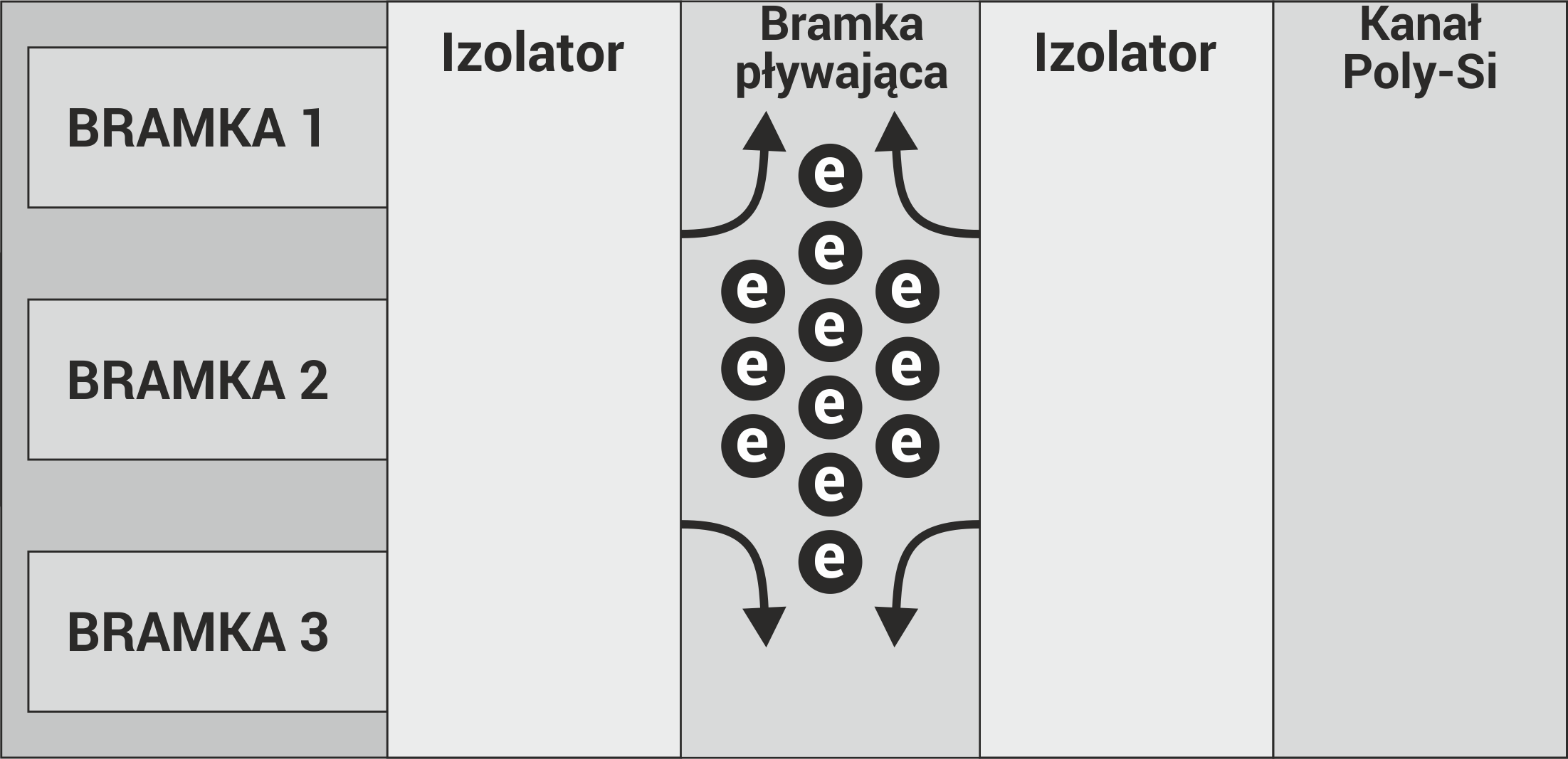

Relatywnie nowa technologia 3D NAND FLASH nie eliminuje wad swojej poprzedniczki 2D. Wprowadza ona nowe wyzwania związane z upływnością w wertykalnej strukturze. W przypadku pamięci 3D można wyróżnić znane z 2D upływności do: kanału tranzystora, bramki, oraz nowe: do warstw pośrednich (ang. spacers), pomiędzy łańcuchami komórek pamięci i poprzez współdzieloną warstwę pływającej bramki (trap layer – rys. 4).

Rys. 4. Upływność pomiędzy sąsiadującymi komórkami pamięci

(rysunek poglądowy, opracowanie własne na podstawie: Micheloni, Rino, Crippa, Luca, Marelli, Alessia, Inside NAND Flash Memories, ISBN 978-90-481-9431-5)

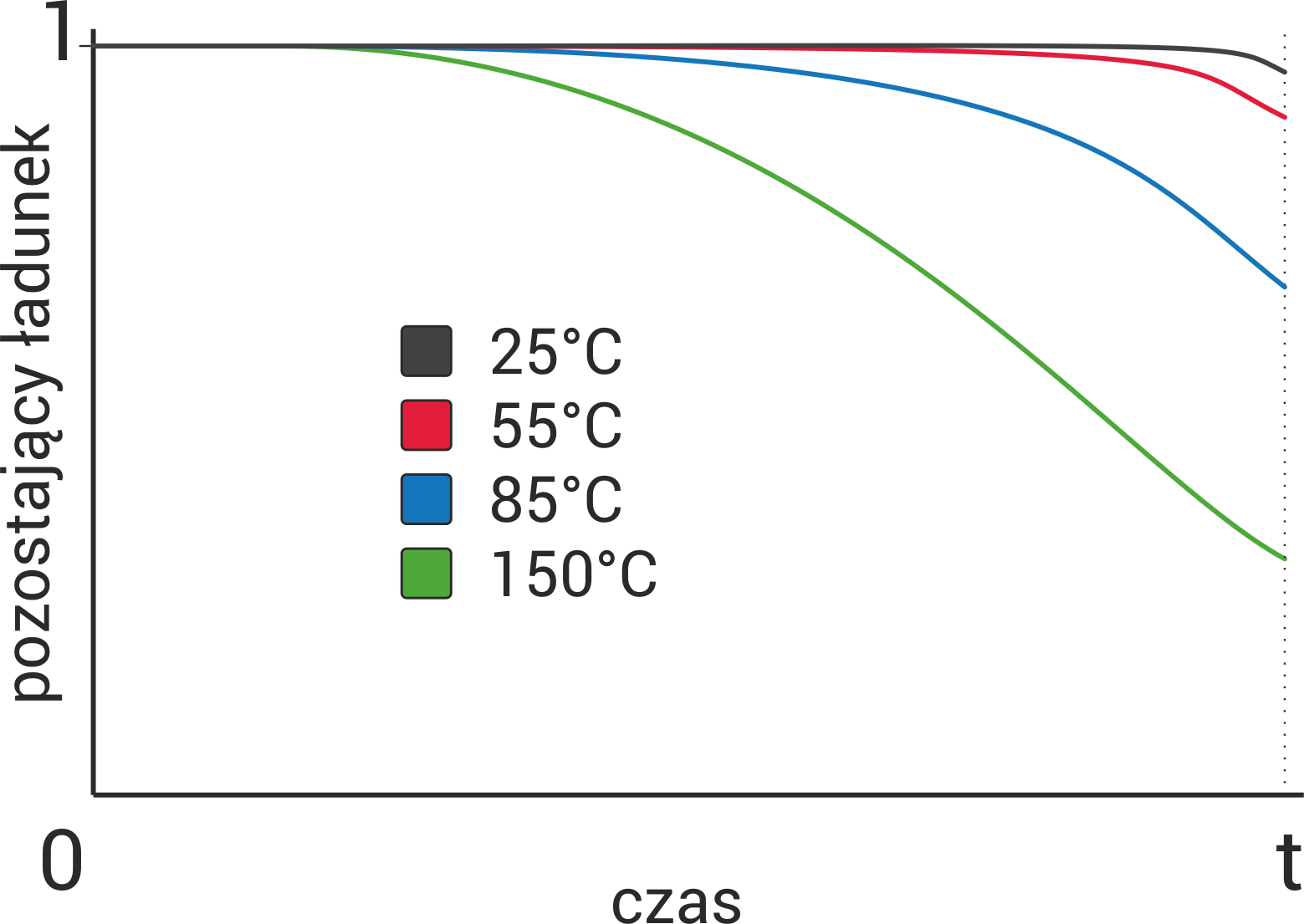

Upływność jest silnie zależna od temperatury co zostało zobrazowane na rysunku 5.

Rys. 5. Trend obrazujący zależność pomiędzy czasem upływności a temperaturą

(opracowanie własne)

Ponadto w strukturach 3D komórki pamięci znajdujące się na górnych warstwach mogą mieć różne wymiary i parametry od komórek znajdujących się na warstwach dolnych. Wszystko to powoduje, że układy pamięci 3D wymagają innych metod detekcji i korekcji błędów niż pamięci typu 2D.

Metody detekcji i korekcji błędów

W pamięciach masowych zbudowanych z zastosowaniem NAND FLASH stosuje się metody detekcji-korekcji BCH lub LDPC. Nazwa BCH pochodzi od nazwisk twórców metody Bose–Chaudhuri–Hocquenghema i jest ona stosowana do detekcji i korekcji błędów w pamięciach typu NAND FLASH 2D (Varsha Regulapati, B.E., Error Correction Codes in NAND Flash Memory, University of Texas at Austin).

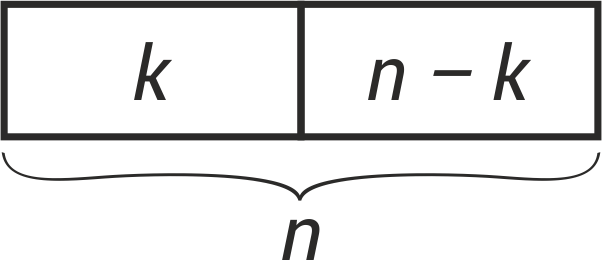

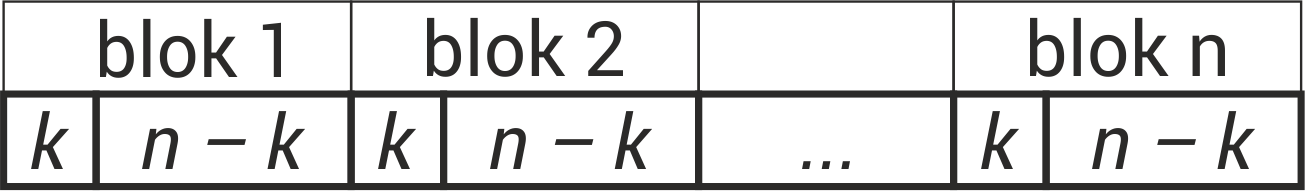

Kody BCH należą do grupy cyklicznych (wielomianowych) kodów blokowych. BCH jest kodem o długości słowa kodowego n, zawierającego k elementów informacji. Liczba elementów kontrolnych wynosi n-k (rys. 6).

Rys. 6. Blok danych z podziałem na k elementów informacji oraz n-k elementów kontrolnych

(opracowanie własne na podstawie literatury).

Każdy zapis danych do dysku, powoduje wygenerowanie przez jego kontroler słów kodowych, a następnie ich zapis w stronach układu pamięci NAND FLASH (rys. 7).

Rys. 7. Przykładowy podział strony układu pamięci NAND FLASH na bloki (sektory)

Jak zauważymy, w trakcie zapisu generowane są elementy kontrolne, zwane bitami „ECC”. Ich zapamiętanie wymaga dodatkowej pojemności układu pamięci. Każda strona układu pamięci NAND FLASH posiada przestrzeń przeznaczaną do tego celu tzw. spare area. Przykładowo, strona pamięci o pojemności 16 kB może posiadać dodatkowo 1 kB przestrzeni nadmiarowej.

W cyklu odczytu słowo kodowe jest odczytywane z układu pamięci, następnie dekoder ustala liczbę bitów zawierających przekłamania oraz ich lokalizację, przekłamane bity są korygowane.

Typowe kontrolery dysków SSD pozwalają na detekcję i korekcję 64-72 bitów w każdym sektorze wielkości 1 kB (pamięci TLC 2D), 24-40 bitów w sektorze 1 kB – MLC 2D. Zdolność BCH do detekcji-korekcji błędów może być ustalona metodami analitycznymi – zupełnie inaczej jest w przypadku kodów LDPC.

Kody LDPC (ang. Low-Density Parity Check) należą do grupy kodów liniowych. Słowo kodowe jest tworzone za pomocą macierzy generującej G. Powstaje ono poprzez przemnożenie wektora danych przez macierz: v = u*G. W przypadku kodów LDPC nieznany jest skuteczny algorytm pozwalający na wyznaczenie odległości Hamminga pomiędzy dwoma słowami kodowymi. Z tego też powodu wyznaczanie przybliżonej skuteczności detekcji i korekcji błędów przez LDPC jest możliwe tylko metodami statystycznymi.

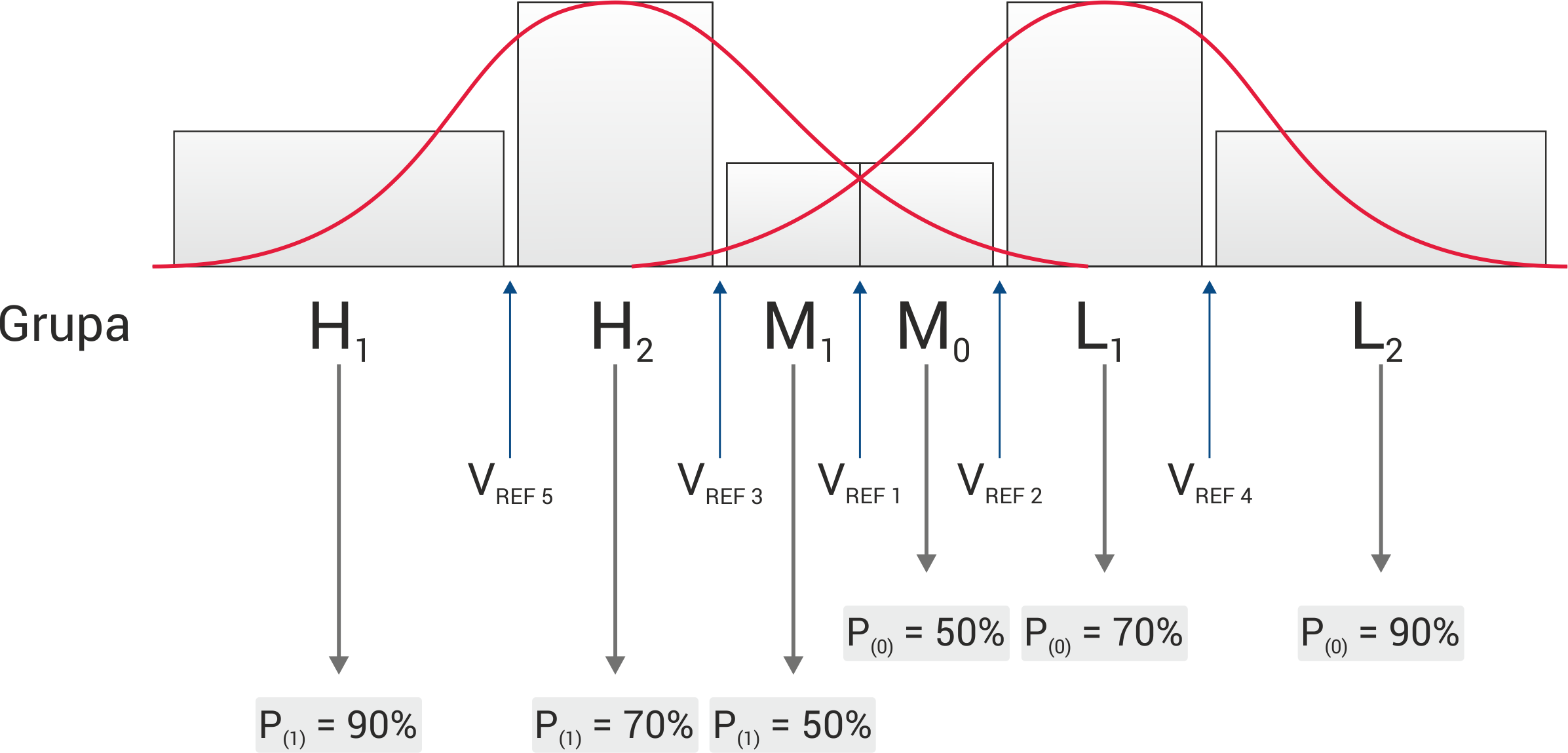

W przypadku LDPC istnieją dwie metody detekcji i korekcji błędów danych. Pierwsza to tzw. „hard decoding”, druga „soft decoding” (SM2258/59 Silicon Motion).

Metoda hard decoding polega na jednorazowym odczycie danych z NAND FLASH i przesłaniu ich na wejście dekodera. Skuteczność detekcji/korekcji tej metody jest nieznacznie wyższa do BCH. W sytuacji, gdy możliwa jest zmiana napięcia referencyjnego Vref i ponowny odczyt danych z NAND FLASH, możliwe jest utworzenie informacji statystycznej wskazującej prawdopodobieństwo występowania błędu (rys. 8).

Rys. 8. Dystrybucja poziomów napięć i prawdopodobieństwo odczytu wartości 0 lub 1

Utworzona statystyka jest wykorzystywana przez iteracyjny algorytm detekcji-korekcji błędów. Algorytm ten podejmuje decyzje o zmianie bitów na przeciwne tj. 0->1, 1->0 dążąc do minimalizacji wagi syndromu błędu.

Zasadniczą zaletą metody soft decoding jest uwzględnienie statystyki charakteryzującej upływność występującą w NAND FLASH. W połączeniu z techniką zapisu pSLC i pMLC, LDPC pozwala na zastosowanie 3D NAND FLASH w wymagających aplikacjach przemysłowych.

Podsumowanie

W związku z ciągłym rozwojem technologicznym granice technologii planarnej zostały już w pewnym stopniu osiągnięte. Niemniej jednak w dalszym ciągu jest ona pożądana na rynku przemysłowym, gdzie istnieje zderzenie dwóch przeciwstawnych potrzeb i interesów. Z jednej strony ograniczona ilość producentów, dla których wytwarzanie produktów 2D jest ekonomicznie nieuzasadnione, z drugiej strony klienci, u których wciąż obserwuje się zapotrzebowanie na rozwiązania 2D, w związku z bardzo dynamicznym rozwojem automatyzacji przedsiębiorstw.

Rozwiązaniem dla powyższego patu jest przedstawienie technologii 3D dla przemysłu, co nie udawało się przez ostatnich kilka lat, bądź skala procesu nie była zadowalająca dla producentów NAND Flash. Jednym z powodów jest proces walidacyjny. Wytwarzane obecnie aplikacje charakteryzują się cyklem życia 5- bądź 10-letnim, co uniemożliwia wymianę tak istotnego elementu jak Flash. Jako drugi z powodów należy wymienić wciąż nie potwierdzoną wytrzymałość i niezawodność technologii TLC 3D na poziomie MLC lub coraz bardziej popularnej w systemach krytycznych – najstarszej, i co za tym idzie najdroższej, technologii SLC.

Zgodnie z przewidywaniami Wilk Elektronik, na przestrzeni kolejnych 5 lat rynek zmieni się diametralnie. Widzimy coraz większe zapotrzebowanie z segmentu przemysłowego na wyższe pojemności nowych produktów – takich jak np. SSD w formacie M.2. Jest to związane z ciągłym rozwojem aplikacji, które istnieją na rynku już od 5, 10, 15 lat. Nastał zatem czas na zmianę rozwiązań typu CFast na technologie oparte o nowszy interfejs – mówi Wiesław Wilk, Prezes Wilk Elektronik.

Z drugiej strony automatyzacja przedsiębiorstw wymusza na właścicielach nowe inwestycje,

w których to właśnie pamięć odgrywa jedną z kluczowych ról. Niestety technologia 2D MLC czy SLC jest coraz słabiej dostępna, a jej koszty rosną, dlatego też rozpoczyna się proces realnego przejścia na 3D TLC, co producenci tacy jak Toshiba dostrzegają i aktywnie wspierają. Nasza firma będzie jedną z pierwszych na świecie, która otrzyma próbki pamięci bazujące na technologii 3D TLC o jakości przemysłowej od firmy Toshiba – zaznacza Prezes firmy. Te, na bazie specjalnego porozumienia podpisanego przez Wilk Elektronik i Toshiba, będą mogły być przełączone w tryby pSLC bądź pMLC, co niewątpliwie ułatwi prace klientom i spełni ich potrzeby. Warto podkreślić, że w perspektywie kolejnych 8 lat, technologia 3D TLC oraz technologie pokrewne będą już wykorzystywane w większości nowych jak i rewalidowanych rozwiązań rynkowych.

Opracowanie:

Wilk Elektronik SA,

Producent pamięci przemysłowych marki GOODRAM Industrial

Tekst ukazał się w postaci artykułu na stronie portalu ElektronikaB2B